HBM에서 가장 중요한 게 TSV 기술인데, TSV 기술은 이제 HBM뿐만 아니라 다른 AI향 메모리에도 필수적인 기술이 되고 있음.

트렌드포스에서 최근자 디램 시황 분석 보고서의 일부를 발췌해 봄.

AI indirectly helps drive up demand, 128 GB high-capacity modules see prices stop falling in April

The

explosive popularity of ChatBOT has driven up demand for AI server

shipments, leading to talks about HBM and boosting purchasing power for

128 GB server DDR5 RDIMM to accommodate ChatGPT 4.0 computing

architecture. This has led to an increase in demand for high-capacity

RDIMMs in early 2Q23, primarily from US CSPs. TrendForce reports that

128 GB RDIMMs require Through-silicon VIA (TSV) packaging, as the DDR5

mono die is mostly 16Gb. However, main suppliers cannot increase their

TSV production capacity in the short term, leading to further price

increases for SK hynix’s high-capacity DDR5 modules this month. This is

in contrast to the current downward trend in the prices of DDR4 and

other DDR5 products.

AI는 간접적으로 디램 수요 증가에 도움이 되고, 128GB 고용량 디램 모듈은 4월에 가격 하락이 멈췄다.

챗GPT의

폭발적인 인기로 AI 서버 출하 수요가 증가하면서, 챗GPT 4.0 컴퓨팅에 필요한 HBM과 128GB 이상 서버향 DDR5

RDIMM 모듈 구매가 증가했다. 이로 인해 주로 미국 CSP를 중심으로 2분기에 고용량 디램 모듈 수요가 증가했다. 128GB

RDIMM 모듈은 DDR5 Die당 용량이 대부분 16Gb인 만큼 TSV 패키징이 필요하다. 다만 주요 공급업체는 단기적으로는

TSV 생산능력을 늘릴 수 없어 이 달 SK하이닉스의 고용량 DDR5 모듈의 가격 상승이 더욱 커졌다. 이는 현재 DDR4 등

DDR5 제품 가격이 하락하는 추세와 대조적이다. (이하 중략)

AI GPU에서 처리하는 막대한 양의 데이터를

입/출력하려면 AI 서버&CPU 모두 훨씬 더 큰 용량의 메모리와 스토리지를 장착해야만 함. 그런 이유로 마이크론이 최근

실적발표회에서 AI 서버는 일반 서버와 비교해 8배의 디램과 3배의 낸드가 필요하다고 말했던 것임.

즉, AI는

단순히 초고성능 메모리(HBM)뿐만 아니라 일반 범용 메모리(특히 디램) 수요 역시 촉진함. 여기에서 제일 중요한 게 128GB

이상 대용량 서버용 DDR5 LRDIMM 모듈임. 서버에도 꽂을 수 있는 디램 모듈 슬롯 개수에도 한계가 있기 때문에 이제는 디램

모듈 당 용량이 증가해야만 하고, 이로 인해서 최소 128GB 이상의 모듈이 AI 서버에 장착되기 때문임. 그래서 4월부터

128GB 이상 대용량 DDR5 디램 모듈 가격은 하락을 멈췄고, 오히려 반등하려는 기미마저 보이는 상황임. 실제로 하닉

컨콜에서도 128GB 이상 대용량 DDR5 디램 모듈의 엄청난 성장세를 언급했음.

이 대용량 디램 모듈을 만드는 데

가장 중요한 기술이 바로 HBM 메모리를 만드는 데에도 쓰이는 TSV(Through Sillicon Via) 기술임. 왜 이

기술이 필요한지를 알려면 서버용 디램 모듈의 구조부터 먼저 이해해야만 함.

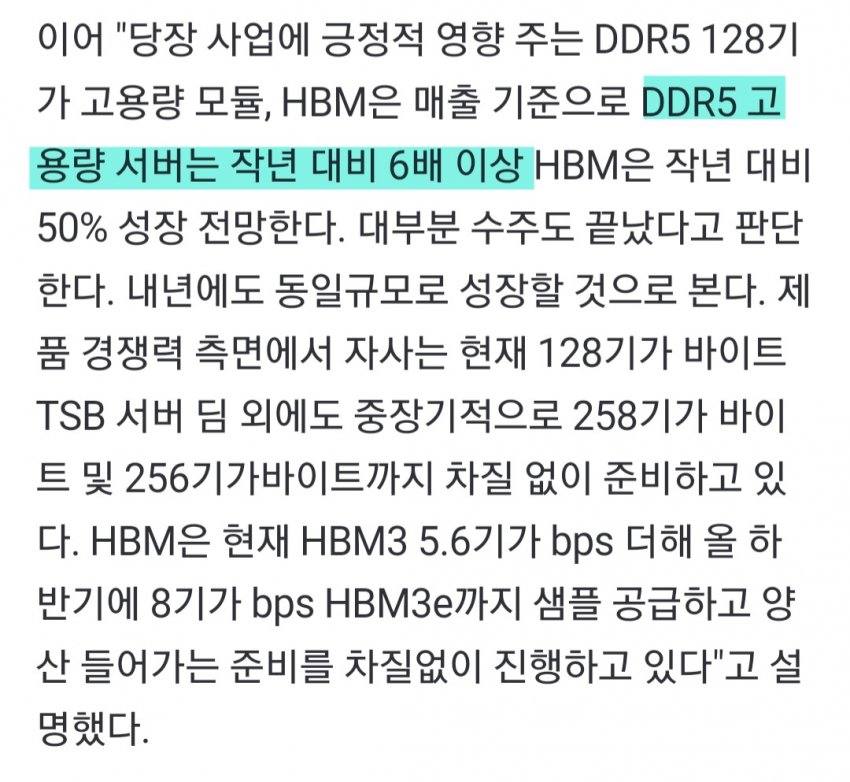

첨부 2가 DDR4/DDR5 서버용 디램

LRDIMM 모듈임. DDR4에는 검은색 칩이 18개, DDR5에는 20개가 장착됨. ECC라고 표시된 칩은 저장 용량에 계산되지

않는 칩임. ECC와 REG에 대해 설명하자면 우선 ECC(Error Correction Code)는 데이터 에러 정정 기능임.

또 REG(Re.gister)는 CPU가 다수의 디램 모듈을 사용할 시, 모듈 간 거리로 인해 미세하게나마 전자 간 이동속도

차이가 발생하여 신호 동기화가 어려워 지는데, 이런 시차를 보정하는 기능임. 이런 보정용 칩이 디램 모듈에 DDR4는 2개,

DDR5는 4개 들어감. 이 보정용 칩을 제외하면 실제 저장 용량용 칩은 16개로 DDR4와 DDR5 모두 똑같음.

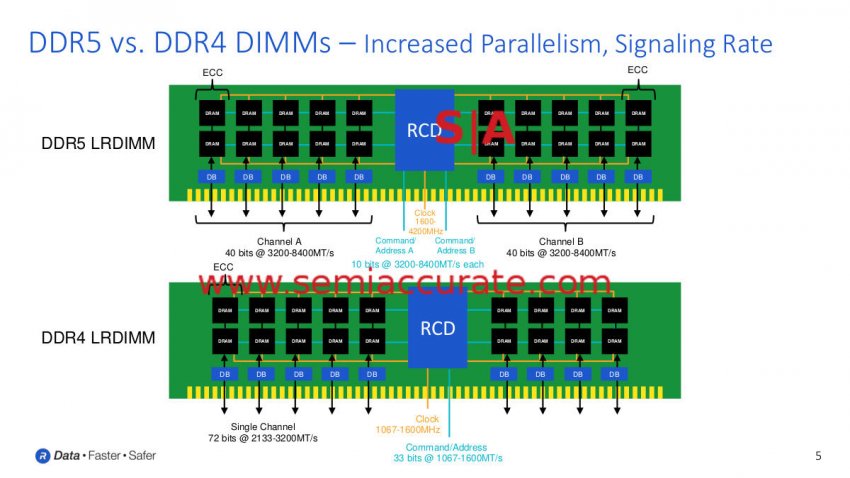

그리고

이 칩을 만드는 패키징 기술에 바로 TSV가 들어감. 첨부 3에 나온 전통적인 Wire Bonding 패키징 기술은 서버용

디램을 만들 때 메모리 Die를 위, 아래 2단 이상으로 쌓기는 어려움. Chip 1하고 Chip 4하고 딱 봐도 Wire 길이

차이가 크지? 이러면 데이터를 입/출력할 때 위, 아래 Die간 속도 차이가 너무 커져서 서버용 디램에 필요한 고성능을 내기

어려움. 그래서 이 Wire Bonding 기술로는 잘해야 2 Stack까지만 가능함. 그런데 위에서 트렌드포스 리포트에서

언급했듯 현재 DDR5 주력 Die가 16Gb이니까 Wire Bonding 2 Stack으로 서버용 디램 모듈을 만든다고

가정하면, 16Gb*2(Stack)*16(저장용 칩)=512Gb=64GB 모듈까지만 만들 수 있음. 그래서 현재 일반적인 서버용

디램 모듈 용량이 32/64GB임.

PS. 여담으로 모바일 디램은 16 Stack까지 무지막지하게 Die를 쌓는

경우가 많음. 왜냐하면 모바일 디램은 퍼포먼스보다 면적을 줄이는 게 훨씬 더 중요하거든. 스마트폰에 들어갈 정도로 아주 작게

면적을 줄여야 하니까 말이지. 예컨대 12GB 모바일 디램은 12Gb Die를 무려 8개나 쌓아서 만든 물건임. 그래서 스마트폰용

LPDDR이 단순 수치로는 DDR 대비 Spec이 좋더라도 실제 체감 성능은 좀 떨어지는 게 이런 이유 때문도 있음. 면적을

줄이기 위해 알게 모르게 감수해야 하는 페널티들이 많거든.

다시 본론으로 들어가면 그래서 현재 주력인 16Gb

Die로 128GB 이상 고용량 디램 모듈을 만들려면 반드시 필요한 기술이 바로 TSV임. Die를 쌓고 Wire가 아니라

수직으로 구멍을 뚫어서 위, 아래 Die를 서로 연결하는 기술임. 이렇게 되면 전자의 이동 거리가 엄청나게 짧아져서 데이터

입/출력 속도가 훨씬 더 빨라질 뿐만 아니라, 전자의 이동 거리가 짧아지니 전력 소모도, 그에 따라 발열 역시 크게 줄어듬.

실제로 같은 용량의 디램 모듈이라고 해도 TSV 기술을 적용한 모듈이 아닌 것보다 작동 전압, 발열, 전력 소모 모두에서 더

성능이 좋음. 그래서 이렇게 TSV 기술로 만든 디램 모듈을 3DS(3D-Stacked) 디램이라고 함.

이렇게

TSV 기술을 적용하면 16Gb Die를 4 Stack 해서 128GB 디램 모듈을 만들 수 있음. 그래서 트렌드포스 리포트에서

"128GB RDIMM 모듈은 DDR5 Die당 용량이 대부분 16Gb인 만큼 TSV 패키징이 필요하다."라고 한 것임. 우선은 이

시장에서 가장 앞서 나가는 게 하닉임. 원래부터 서버용 디램을 잘 만들었었고, 1anm DDR5 서버용 대량생산 인증도 제일

빨랐고, HBM3에서도 드러났듯 TSV 공정 기술력도 제일 뛰어나기 때문임. 반대로 가장 뒤쳐지는 것은 마이크론이라고 생각함.

하닉과 정 반대 상황임. 애초부터 서버용 디램에 약했고, 그러다 보니 삼성증권 리포트에서도 나왔듯 1anm DDR5 서버용

대량생산 인증도 가장 늦고, HBM에서도 드러났듯이 TSV 공정 기술력도 가장 뒤쳐지기 때문임. 여담으로 지금 하닉은 TSV

CAPA가 HBM3 주문 대응하는 것만으로도 부족해서 128GB 이상 디램 모듈 가격을 올려받으려고까지 하는 상황임.

그래서

삼전이 준비한 필살기가 바로 1bnm 32Gb DDR5 디램임. 1bnm 공정으로 만든 Die당 용량이 32Gb짜리 DDR5

디램이라는 뜻임. 현재 주력인 16Gb Die로는 TSV 공정을 써야만(4 Stack) 128GB 디램 모듈 제작이 가능하다면,

32Gb Die는 2 Stack만 해도, 그러니까 Wire Bonding만 해도 제작이 가능해서 비용 절감과 생산성 향상 둘 다

잡을 수 있거든.

그렇다면 여기에서 들 수 있는 의문이 있음. "아니, 16Gb Die가 아니라 32Gb Die로

만드는 게 이득이라면 그냥 현재 양산중인 1anm나 1znm 공정으로 32Gb DDR5 생산하면 안 됨?"인데, 그게 힘듬. 왜?

Wafer의 면취효율 때문임.

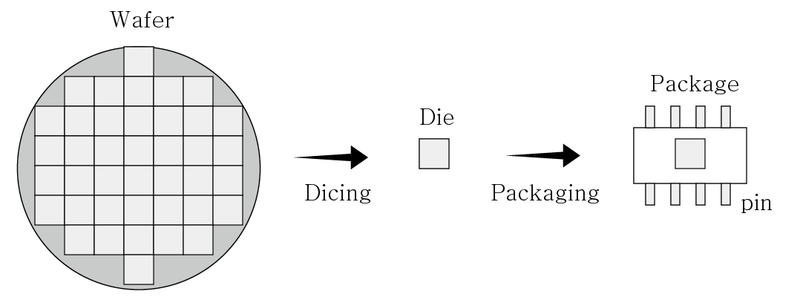

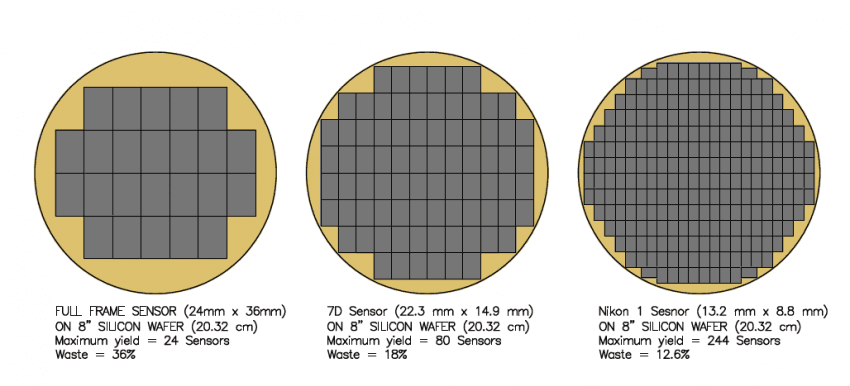

첨부 5가 Wafer를 Die 단위로 잘라서 패키징해서 칩을 만드는 프로세스이고,

첨부 6이 Die 크기 차이로 인한 Wafer 면적 손실률(노란색 부분)을 나타냄. 예를 들어 8인치 Wafer 기준으로 Die

사이즈가 24nm*36nm라면 Die는 최대 24개 만들 수 있고 Wafer 면적은 36%를 손해봄. 그리고 Die 사이즈가

작아질수록 이 손실률은 계속 작아져서 Die 사이즈 13.2nm*8.8nm가 되면 면적 손실률은 12.6%까지 줄어듬. 그리고

결정적으로 같은 면적에서 불량이 발생했다고 치면 그로 인해 버려야 할 Die 사이즈가 훨씬 더 커지니까 수율 Loss도 훨씬

커짐. 즉, 충분히 선폭이 줄어들지 못한다면 무작정 Die 크기를 키우는 것은 생산 과정에서 손실이 너무 큼.

그래서

1anm와 1znm 공정으로는 32Gb Die를 만드는 건 너무 비효율이 크고, 적어도 1bnm 공정까지는 가야만 그나마

생산성이 나옴. 지금 같은 다운턴에서는 다른 경쟁사들은 투자 여력이 없어서 1bnm 공정 전환이 어렵고, 그래서 당분간은 삼전만

유일한 1bnm 32Gb DDR5 공급자로 남을 수 있음. 그래서 첨부 7에도 나왔듯 삼전 컨콜에서 1bnm 32Gb 제품 개발을

그렇게도 강조하는 것임. 그리고 이 32Gb DDR5 제품에 TSV 공정까지 적용하면 업계에서 유일한 256GB 디램 모듈의

대량 공급자로 남을 수 있게 됨. 이 때문에 삼전의 필살기가 1bnm 32Gb DDR5 디램이라는 것임.

반대로

Die 크기가 작을수록 면취효율이 높다면 그냥 8Gb Die로 TSV 공정으로 8 Stack 해서 128GB 디램 모듈을 만들면

안되냐고 할 수 있는데, 그렇게 되면 TSV 공정의 난이도가 너무 올라감. 건물을 높게 쌓을수록 건설 난이도가 기하급수적으로

올라가는 것과 비슷함. 그리고 4개 쌓다가 공정에서 불량나면 Die 4개만 죽이면 되지만 8 Stack은 8개나 죽여야 해서 수율

손실도 너무 큼. 그래서 TSV 공정으로 8 Stack 이상은 정말로 초고성능 퍼포먼스가 중요한(무조건 성능>가격인)

HBM에만 적용하고 있음. 그런데 앞으로 TSV 공정도 기술력이 더 좋아지면 32Gb Die를 8 Stack해서 1TB 초대용량

디램 모듈을 만들 수도 있겠지.

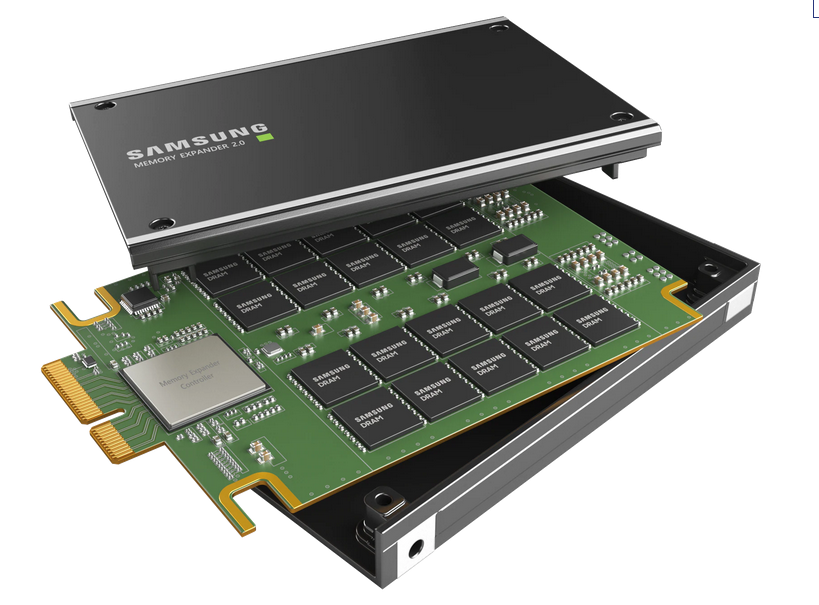

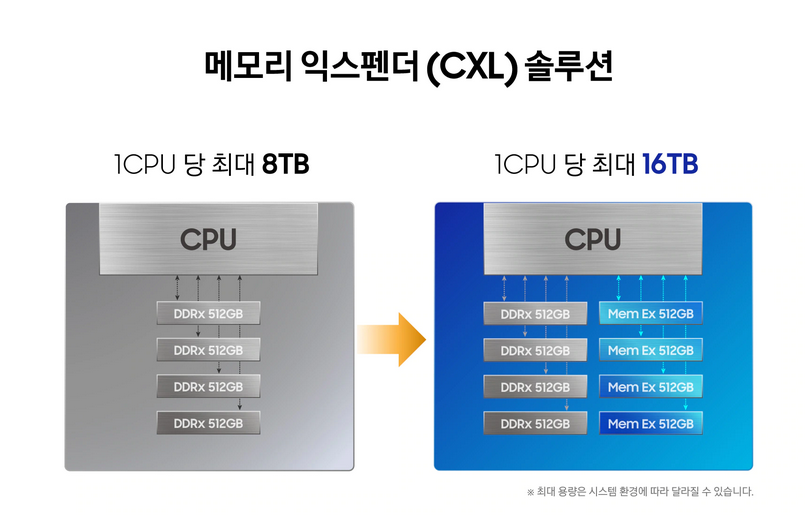

마지막으로 이제는 CXL도 매우 중요해지고 있음. 첨부 8~9에 나왔듯 CXL은

SSD Pcie 슬롯에 디램 모듈을 장착할 수 있게 함으로서 호환성과 CPU 당 디램 용량을 크게 늘려주고, 또 SSD처럼

컨트롤러를 탑재해서 대용량 디램의 데이터 관리를 보다 쉽게 해 주는 새로운 디램 모듈 규격임. CXL과 TSV 기술이 결합하면 수

TB 이상의 디램 모듈 제작이 가능해짐. 이렇게 되면 AI 서버 당 수백 TB 이상의 디램이 탑재되어 상상 이상의 초고성능

연산이 가능해짐.

그래서 나는 메모리, 디램의 미래를 매우 좋게 봄. 지금의 다운턴은 일시적일 뿐임. AI가 이끌

챗GPT와 자율주행이라는 새로운 산업혁명의 중심에 디램이 있기 때문임. 하단에 첨부한 옴디아 리포트에서 24년 이후 강력한 디램

호황 사이클이 올 것이며, 또 디램이야말로 AI의 가장 강력한 수혜를 받을 것이라고 주장하는 게 바로 이 때문이며, 나도 이

주장에 매우 동의함.